模擬CMOS集成電路設(shè)計 從基礎(chǔ)原理到實際應用

模擬CMOS集成電路設(shè)計是現(xiàn)代電子工程的核心領(lǐng)域之一,廣泛應用于通信系統(tǒng)、傳感器接口、電源管理和音頻處理等領(lǐng)域。隨著半導體技術(shù)的不斷進步,模擬CMOS設(shè)計在實現(xiàn)高精度、低功耗和高速性能方面發(fā)揮著關(guān)鍵作用。本文將從模擬CMOS集成電路的基礎(chǔ)原理、設(shè)計流程、關(guān)鍵挑戰(zhàn)以及未來發(fā)展趨勢等方面進行探討。

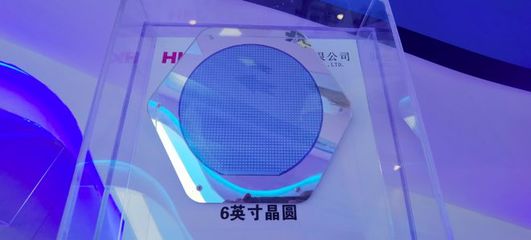

模擬CMOS集成電路設(shè)計依賴于互補金屬氧化物半導體(CMOS)技術(shù),該技術(shù)通過結(jié)合NMOS和PMOS晶體管來實現(xiàn)高效的信號處理。設(shè)計者需要深入理解器件物理特性,如閾值電壓、跨導和輸出電阻,這些參數(shù)直接影響電路的性能。模擬電路通常處理連續(xù)時間信號,與數(shù)字電路不同,它更關(guān)注線性度、噪聲、帶寬和功耗等指標。

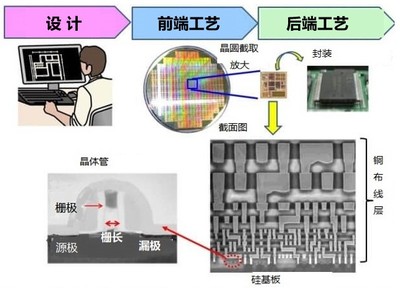

設(shè)計流程一般包括需求分析、電路拓撲選擇、仿真驗證、版圖設(shè)計和測試驗證。在需求分析階段,設(shè)計者需明確電路的功能規(guī)格,如增益、帶寬和電源電壓。選擇適當?shù)碾娐吠負洌邕\算放大器、比較器或數(shù)據(jù)轉(zhuǎn)換器,并使用仿真工具(如SPICE)進行性能評估。版圖設(shè)計是關(guān)鍵步驟,需要考慮寄生效應、匹配問題和熱管理,以確保電路的可靠性和良率。通過實際測試驗證設(shè)計是否符合預期。

模擬CMOS設(shè)計面臨的主要挑戰(zhàn)包括工藝變異、噪聲干擾和功耗優(yōu)化。隨著工藝節(jié)點縮小,器件的不確定性增加,設(shè)計者必須采用魯棒的設(shè)計方法,如使用反饋結(jié)構(gòu)和校準技術(shù)。低功耗設(shè)計在物聯(lián)網(wǎng)和移動設(shè)備中尤為重要,這需要平衡性能與能耗。

模擬CMOS集成電路設(shè)計將朝著更高集成度、更智能的自動化工具和新興應用(如人工智能硬件和生物醫(yī)學設(shè)備)發(fā)展。設(shè)計者需不斷學習新技術(shù),以適應快速變化的市場需求。模擬CMOS設(shè)計不僅是技術(shù)挑戰(zhàn),更是創(chuàng)新的源泉,推動著電子行業(yè)的進步。

如若轉(zhuǎn)載,請注明出處:http://www.dongxiaojing.cn/product/38.html

更新時間:2026-04-20 07:57:57